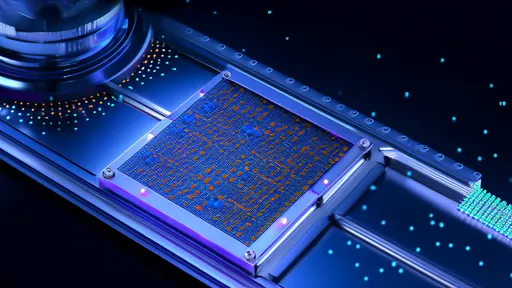

The rapid evolution of artificial intelligence and edge computing has placed unprecedented demands on data processing efficiency. Among the emerging technologies addressing this challenge, in-memory computing (IMC) has gained significant traction for its ability to perform computations directly within memory arrays, eliminating the von Neumann bottleneck. A critical aspect of IMC systems is their analog-to-digital conversion (ADC) precision, which fundamentally determines the reliability and accuracy of the entire computing paradigm.

Understanding the Precision Challenge in IMC ADCs

Unlike traditional computing architectures where data shuttles between separate memory and processing units, in-memory computing performs matrix-vector multiplications in analog domain within the memory array itself. This approach requires highly precise ADCs to convert the analog computation results back into digital signals. The precision of these converters directly impacts the system's computational fidelity, especially in deep learning applications where slight errors can propagate through neural networks.

The quest for higher ADC precision in IMC systems faces several fundamental constraints. Memory devices themselves introduce variations due to fabrication imperfections, and the analog nature of computation accumulates noise. Moreover, the dense integration of memory cells leaves limited area for high-resolution ADCs, creating an intrinsic trade-off between precision and area efficiency. Researchers are exploring various architectural innovations to break through these limitations while maintaining the energy efficiency advantages of IMC.

Emerging Solutions and Architectural Innovations

Recent breakthroughs in ADC design specifically tailored for in-memory computing have shown promising results. One approach involves distributed low-resolution ADCs combined with advanced digital signal processing techniques. Instead of relying on a single high-precision converter at the array periphery, this method employs multiple coarse ADCs that work in concert, with their outputs digitally combined to achieve the desired precision. This architecture significantly reduces area overhead while maintaining conversion accuracy.

Another innovative direction focuses on time-domain ADCs that leverage the temporal characteristics of signals rather than amplitude measurements. These converters offer better scalability with technology nodes and demonstrate superior noise immunity compared to conventional voltage-domain approaches. Some implementations have achieved 8-bit precision with remarkable energy efficiency, making them particularly suitable for IMC applications where power consumption is paramount.

The integration of machine learning techniques into ADC calibration represents yet another frontier. Adaptive algorithms can learn and compensate for systematic errors in real-time, effectively boosting the effective resolution beyond the nominal hardware capabilities. This software-hardware co-design approach has demonstrated the potential to achieve 10-bit effective precision using 6-bit physical ADCs in certain IMC implementations.

Material and Device-Level Advancements

Beyond architectural innovations, breakthroughs in materials science are enabling higher precision in IMC ADCs. The development of novel memristive devices with improved uniformity and linearity characteristics directly enhances the quality of analog signals feeding into the converters. Some research groups have demonstrated that certain ferroelectric materials can provide more stable and predictable resistance states, reducing the burden on subsequent ADCs.

At the device level, the emergence of hybrid ADCs that combine the strengths of different conversion techniques shows particular promise. For instance, integrating successive approximation register (SAR) architectures with delta-sigma modulation creates converters that achieve high precision without excessive power consumption. These hybrid designs are proving especially valuable for IMC systems targeting inference applications in resource-constrained edge devices.

Advanced packaging technologies also contribute to improved ADC performance in IMC contexts. By implementing ADCs in separate chips that are tightly integrated with memory arrays through 3D stacking or advanced interconnects, designers can optimize each component independently while maintaining the benefits of in-memory computing. This approach alleviates some of the area constraints while enabling better thermal management for precision-sensitive analog circuits.

Benchmarking and Application-Specific Optimization

The evaluation of ADC precision in IMC systems requires specialized metrics that account for the unique characteristics of analog computing. Traditional figures of merit like effective number of bits (ENOB) must be complemented with application-aware measurements that reflect the actual impact on computational accuracy. Researchers have developed new benchmarking frameworks that assess ADCs in the context of complete neural network inference tasks rather than isolated performance.

Application-specific optimization has emerged as a powerful strategy for balancing ADC precision with other system requirements. For computer vision tasks, certain studies have shown that non-uniform quantization schemes can deliver superior results compared to linear ADCs with higher nominal precision. This insight has led to the development of configurable ADC architectures that can adapt their characteristics based on the workload, achieving optimal precision where it matters most for the specific application.

The relationship between ADC precision and neural network architecture presents another dimension for optimization. Some researchers are co-designing neural network topologies that are inherently robust to ADC imperfections, effectively reducing the precision requirements without sacrificing model accuracy. This holistic approach to system design promises to push the boundaries of what's achievable with practical IMC implementations.

Future Directions and Industry Adoption

As in-memory computing transitions from research labs to commercial products, ADC precision remains a key differentiator among competing implementations. Industry leaders are investing heavily in developing proprietary ADC solutions that balance precision, power, and area considerations. Some companies have begun offering IMC chips with configurable ADC precision, allowing users to trade off computational accuracy against energy consumption based on application needs.

The coming years will likely see continued innovation in ADC architectures specifically optimized for IMC applications. Emerging technologies like photonic ADCs and quantum-inspired conversion techniques may offer new pathways to overcome current limitations. Meanwhile, the growing ecosystem of tools for simulating and characterizing ADCs in IMC contexts will accelerate the design of more efficient solutions.

Ultimately, the progress in ADC precision for in-memory computing will play a pivotal role in determining how broadly this paradigm gets adopted across different segments of the computing landscape. From ultra-low-power edge AI to high-performance data center applications, the ability to maintain computational accuracy while leveraging the inherent efficiency of in-memory architectures will continue to drive research and investment in this critical area of mixed-signal circuit design.

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025