The RISC-V ecosystem has been gaining significant traction in recent years as an open-source alternative to proprietary processor architectures. One of the critical areas of development within this space is security monitoring, particularly as RISC-V moves into more sensitive applications. The RISC-V security monitoring architecture represents a paradigm shift in how hardware-level security can be implemented in an open-standard environment.

Understanding the RISC-V Security Landscape

Unlike traditional architectures where security features were often bolted on as afterthoughts, RISC-V was designed with security as a foundational consideration. The security monitoring architecture takes this a step further by providing hardware-level mechanisms for detecting and responding to potential threats. This approach is particularly relevant in today's computing environment where sophisticated attacks often bypass software-only security measures.

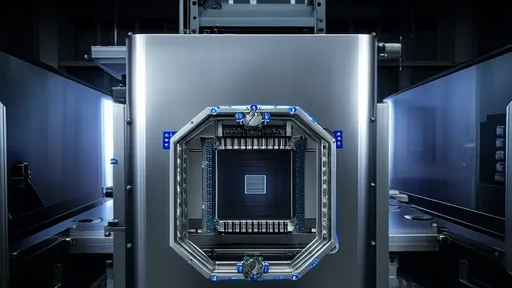

The architecture implements several innovative concepts that differentiate it from conventional solutions. Rather than relying solely on software-based monitoring, it incorporates dedicated hardware components that can operate independently of the main processor cores. This separation creates what security experts call a "hardware root of trust" - a fundamental security primitive that can't be compromised through software vulnerabilities alone.

Key Components of the Monitoring Architecture

At the heart of the RISC-V security monitoring architecture lies the concept of privilege levels and physical memory protection. The architecture defines multiple privilege modes that create logical isolation between different security domains. What makes this implementation unique is how these privilege levels interact with the monitoring components to create a comprehensive security fabric.

The physical memory protection unit (PMP) plays a crucial role in this architecture. Unlike traditional memory protection schemes, the RISC-V implementation allows for fine-grained control over memory regions at the hardware level. This means security policies can be enforced even if the operating system or hypervisor becomes compromised. The monitoring components can detect unauthorized access attempts and trigger appropriate responses without software intervention.

Real-world Applications and Implications

Industrial implementations of this architecture are already showing promise in several critical sectors. In automotive systems, where functional safety and security are paramount, RISC-V-based security monitoring helps protect against both accidental faults and malicious attacks. The deterministic nature of the hardware monitoring makes it particularly suitable for safety-critical applications where response times must be guaranteed.

The architecture's flexibility also makes it attractive for cloud computing environments. Cloud service providers are exploring RISC-V solutions to create more secure multi-tenant environments where hardware-level isolation can prevent lateral movement by attackers. This could potentially address some of the most challenging security problems in shared computing infrastructure.

Challenges and Future Directions

While the RISC-V security monitoring architecture offers numerous advantages, it's not without challenges. The open nature of RISC-V means implementations can vary significantly between vendors, potentially leading to compatibility issues. Standardization efforts are ongoing to ensure a consistent security baseline across different implementations while still allowing for innovation.

Another area of active development is the integration of machine learning techniques into the monitoring architecture. Researchers are exploring how anomaly detection algorithms can be implemented in hardware to identify sophisticated attack patterns that might evade traditional rule-based monitoring. This represents an exciting frontier in hardware security that could redefine how we think about processor-level protection.

The evolution of RISC-V security monitoring continues at a rapid pace, with new extensions and improvements being proposed regularly. As the architecture matures and sees broader adoption, it has the potential to set new standards for what's possible in hardware-assisted security. The coming years will likely see these technologies move from research labs into mainstream computing devices, potentially reshaping the security landscape across multiple industries.

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025

By /Aug 7, 2025